(林宗輝/DigiTimes.com) 2005/12/27

導言:最新的CPU運算科技以及最先進的即時3D繪圖技術的展示平台在何處?不是企業伺服器,也不是家用電腦,而是在遊樂器平台上,3大遊樂器主機廠商戰事方興未艾,其中以Sony應用在PS3上的Cell處理器技術最讓眾人注目。

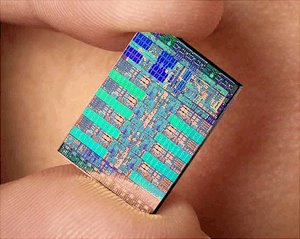

圖說:Cell處理器的問世,代表著全新一代的運算技術正式登場。

前言

2005 年,全球遊戲市場產值已經突破了280億美元(IDC調查報告數據資料),3大遊戲主機廠商分別都推出了新世代主機計畫,在硬體的設計概念上雖大異其趣,但是在核心組件上,確有著不小的共通點,如今微軟Xbox360先走1步,意圖搶佔市場先機,然而Sony將上市的PS3卻如芒刺在背,讓微軟如坐針氈。

即使是邁向邊緣化的任天堂,雖然在硬體性能上偏弱勢,卻有著非常突出的遊戲思維。然而Sony與其他兩家遊樂器廠商不同的是,PS3代表的不只是次世代的遊樂器平台,更是推展Cell技術與Blu-Ray Disc的一個里程碑。

Cell的起源

Sony 自從加入遊樂器市場之後,所採用的都是RISC架構的中央處理器,從PS1時代與LSI公司合作的R3000A,與Toshiba及LSI兩大公司合作,為PS2設計了基於MIPS架構的Emotion Engine,到了次世代主機PS3上,更是結合了Toshiba以及IBM公司的力量,組成了STI陣營,從2001起年投入Cell處理器的研發工作,到2005年正式產品面世為止,總共歷時約5年,Cell處理器不止代表了Sony力圖在遊樂器市場上維持霸主的地位,同時也讓Toshiba及 IBM這兩大盟友在各自的領域獲得助益。

過去處理器世界分為精簡指令集以及複雜指令集兩大陣營,並且互相對抗,複雜指令集自然是以 Intel的X86處理器為首,精簡指令集這邊則是以PowerPC為大宗,並加上其他如SPARC、ALPHA等使用於高階伺服器的專用處理器, Apple、IBM以及Motorola所組成的AIM陣營過去一直在精簡指令集這塊市場耕耘,但是到了最後,由於微軟的刻意忽略,消費者的市場慣性,加上傳說中支援X86指令集的PowerPC 615難產,Apple轉而與微軟合作爭取支援,並將旗下Mac電腦改採用Intel處理器,而Motorola則是將處理器部門獨立出來, PowerPC架構只留下IBM獨力發展。

而IBM也一改過去提供各種類處理器產品給客戶的作法,改為全力經營PowerPC這一塊處理器市場,並針對不同的客戶需求,進行PowerPC的各種客製化動作,比如說,供應給微軟Xbox360的3核心XCPU,任天堂Revolution 主機所使用的雙核心Broadway處理器,都是基於PowerPC所演化出來的架構,基本上其所有權皆歸屬於IBM,後來與Sony及Toshiba合組的STI陣營,聯合研發Cell處理器,由於IBM處理器部門的長期虧損,這次聯合研發Cell處理器,也頗有背水一戰的感覺。

STI三大巨頭的合作模式

STI 是由Sony、Toshiba以及IBM所聯合組成,主要使命在於研發Cell處理器,其實在Cell之前,IBM就曾經提供了改版自PowerPC的 Gekko處理器供任天堂的GameCube使用,這也是IBM首次跨足遊樂器中央處理器市場。GameCube除了被公認為硬體設計非常的均衡之外,藉由IBM的技術支持,提供了相關的軟體開發套件,因此GameCube的軟體開發也變的相對簡易,雖然GameCube並沒有在遊樂器市場上取得絕對多數,但是與後起之秀的微軟Xbox仍然打了個五五波。

Sony與IBM的合作也是著眼於此,藉助IBM的軟體開發技術,意圖一掃過去PS2時代因為硬體刁鑽,加上開發函式庫的不完整,致使遊戲開發商難以開發的缺點,基本上,完備的軟體開發套件可以大幅降低遊戲開發的時程以及成本。

除了PowerPC技術以及軟體開發上的訴求外,IBM還擁有1個很大的優勢,SOI、銅製程以及應變矽技術可以說領先於全球半導體產業,絕緣矽(Silicon on Insulator;SOI)技術是由IBM研發成功,主要是在矽晶片下添增氧化物的絕緣層,避免電氣效應,以降低電源消耗,減少電流的流失,加快IC的處理速度。

應用到Cell處理器上的製程技術包含了SOI技術以及應變矽技術,應變矽技術是指強迫矽晶格稍做伸展(約1%),穿過晶格的電子遷移率會提高不少,建築在矽之上的電晶體因而得以操作得更快。為了將應力加入矽,晶片製造商將它與其他晶格間距較大的結晶材料結合,比如說採用矽鍺混合物,許多製造商已經採用了這種做法。例如英特爾公司在2004年底上市名為Prescott的Pentium 4 Extreme,就使用了應變矽。Cell在導入這兩項製程技術之後,可以確保在高頻化時代,於超高的效能表現下仍可以維持合理的電力消耗及溫度。

與Toshiba的合作則是另一個相當有趣的案例,Sony與Toshiba在次世代藍光光碟的競爭上是處於水火不相容的對立狀態,卻在半導體晶片上擁有緊密的合作關係,可見在商場上並沒有絕對的敵我。從過去PS2 Emotion Engine與Toshiba合作以來,Cell算是兩家公司第二次合作了,Sony需要Toshiba的XDR記憶體和eDRAM製造技術支持(雖然最後Cell構並沒有引入eDRAM),而Toshiba則是對可應用於HDTV中的Cell嵌入式版本,以及IBM、Sony兩大公司的半導體技術及資金相當有興趣,這幾個相互的利益關係也促成了這次的合作。

Cell核心系統架構-跨越傳統CPU設計的思維

過去CPU 設計的目標不外乎是在每一個執行週期執行越多的指令,要不然就是拼命的將時脈拉高,在Pentium 4時代,由Intel主打的時脈戰爭,在行銷手段上不斷灌輸給消費者時脈高就是快的觀念,但是到最後,由於耗電量與發熱量得不到解決,到最後甚至宣告放棄 Pentium 4 NetBurst架構,NetBurst架構由於著眼於串流技術應用,在SIMD方面藉由SSE3等技術,在多媒體方面有著不錯的成績,不過串流應用只佔了全部PC應用的一部分而已,也因此讓AMD公司有可乘之機,在遊戲以及辦公室應用上的運算效能,狠狠的壓倒Intel。

不過並不是管線深效率就一定會差,管線加深,那麼CPU的分支預測演算法及快取記憶體的設計分配就會變的極端重要,Intel當初錯估了形勢,將SIMD等串流應用優先度擺太高,在分支預測的設計上正確度不夠高,造成指令猜錯回取的次數過高,加上管線深,指令要重新填滿管線花費的時間太高,也因此造成了許多應用的運算處理上效能不彰,Cell的管線階層跟Pentium 4差不多深,但是藉由雙issue指令派發,以及執行緒的動態負載功能,加上Cell應用程式的特殊性,因此在分支預測的效率可以得到非常好的解決。

除了CPU本身架構以外,匯流排的設計也是一大瓶頸,在實際應用中,絕大部分的CPU效能增長都會被緩慢的周邊所拖累,傳統PC架構裡,記憶體與CPU之間的傳輸動作都會有高達數千個CPU週期的延遲,這對運算效能而言是個非常嚴重的浪費,即使提升了記憶體的時脈或加大傳輸頻寬,改善的程度仍然不明顯,所以在桌上型電腦的世界裡,AMD將記憶體控制器內建到CPU晶片中,並透過HyperTransport架構溝通,大幅改善了過去被詬病的記憶體延遲現象。Cell架構中,則引入了Flex I/O架構,有效擴大了CPU與記憶體和繪圖晶片之間的通道。

那麼STI是如何去設計Cell 架構的呢?Cell處理器當初發布時,是定位在網路處理器,在最主要的核心部分,是採用64位元PowerPC核心,每週期2指令派發的超純量架構,擁有 512KB快取記憶體,官方命名為PPE(Power Processor Element)。PPE內建了Fine-grained多執行緒架構,可以在2個執行緒中動態偵測指令的密度,處理器會平均在2條執行緒中抓取指令,當 2條執行緒中有1條過於空閒時,處理器就會自動會拉高另1條執行緒丟指令的速度,提升的幅度約從雙週期1個指令拉高到每週期1個指令。

多執行緒應用在向Cell這種管線階層深的處理器上,其效用非常明顯,由於管線深,如果其中1個執行緒發生了分支預測失敗,那麼重新取得指令回填管線的時間延遲將會非常巨大,就Cell的PPE來說,分支預測失敗的話,會有8個週期的管線效能損失,以及4個週期的快取記憶體存取時間損失,採用多執行緒之後,如果其中1條執行緒出現分支預測失敗,這時處理器就可以全力處理另1條執行緒的指令,讓另1條執行緒可以有時間將預測失敗所損失的時間補回來。

圖說:PPE在1個時脈週期內可以同時預取4個指令,並派發兩個指令,為了加強在其in-order管線處理上的效率,PPE使用了延遲執行管線,並可以允許有限制的載入out-of-order指令的方式執行,因此在out-of-order的執行上,可以不需要太複雜的設計即可取得良好的效能增加。(圖片來源/IBM網站)

除了PPE這位老大以外,Cell處理器之中還包含了8個跟班,這些跟班叫做Synergistic Processor Elements,簡稱SPE,也可以稱作Synergistic Processor Unit(SPU),這8個SPE都是具有256KB Local Store SRAM以及記憶體流量控制器(MFC,但實際上做的是DMA的動作)的處理單元,雖然只有256KB,不過Local Store可以稱做是SPE的主記憶體,而不是快取記憶體,因為Local Store記憶體的存取都必須透過軟體來控制。

SPE是基於SIMD的處理單元,每個SPE都是針對32位元單精度最佳化的4路SIMD處理單元,雖然SPE也支援雙精度浮點計算,但是性能會降到約1/10,每個SPE之中包含有128個超低延遲的128位元暫存器,暫存器數量的龐大,也可以有效降低存取Local Store的次數,SPE的指令集源自於PowerPC的向量擴展VMX/AltiVec和PS2 Emotion Engine的向量單元指令集,在極限狀態下,8個SPE可以在4GHz的時脈下,提供高達256GFlops的運算能力,拿實際的例子來說,IBM在 2005年11月30日所公布的效能測試報告中指出,單一SPE處理單元即可以每秒77頁的畫面張數,處理18Mbit/s流量的HDTV MPEG 2串流解碼。

圖說:SPE的SIMD指令可以同時操作16個8bit整數、8個16bit整數以及4個32bit整數,或是單週期4個單精度浮點運算,在3.2GHz的運作時脈下,可以提供高達25.6Gflop/s的單精度運算。在這張圖中,我們可以看到每個處理單元的配置狀況,當1 組被預取的指令集中,擁有2個可以被派發的指令時,SPE就會啟動雙重指令派發,其中1個指令會被Even Pipeline執行,而另1個指令則會送往Odd Pipeline執行。(圖片來源/IBM網站)

有了這麼強力的計算核心,當然也需要在匯流排上作文章,記憶體子系統要能滿足Cell的資料讀寫需求,那麼Cell的處理效能也才有發揮的餘地。Cell的I/O以及記憶體子系統都是由 RAMBUS取得授權的技術。做為主記憶體使用的XDR記憶體子系統,擁有兩組記憶體控制器,能提供25.6GB/s頻寬,相較起目前PC主流DDR及 DDR2記憶體3.2GB到6.4GB的頻寬,其差距不可謂不大。

而Cell與繪圖晶片之間的通道,則是採用FlexI/O技術, FlexI/O提供了7組TX(信號發送)8bit通道(Lane)和5組RX(信號接收)8bit通道,每條通道在4GHz傳輸速率下提供的傳輸頻寬是 3.2GB/s,合共38.4GB/s的I/O頻寬。依照目前Cell運作的時脈來估算,讀取速度可達20GB/s左右,而寫入則是15GB/s,大大超越了目前PC平台上主流的PCI Express 16x的4GB/s上下傳輸速率。Cell的FlexI/O是為雙處理器SMP設計的,如果想連接更多的Cell還需要增加1個HUB才行(4個Cell 配1個Hub,設計上為光纖Hub)。

沒有留言:

張貼留言